# Towards determining the optimal ion implantation temperature & beam current, annealing temperature & time, in SiC device manufacturing

V. Boldrini<sup>1</sup>, M. Canino<sup>1</sup>, M. Pieruccini<sup>1</sup>, R. Chebi<sup>2</sup> & J. A. Turcaud<sup>2</sup>

<sup>1</sup> CNR Institute for Microelectronics and Microsystems, Via Gobetti, 101, Bologna, 40129, Italy

<sup>2</sup> Coherent Corp., 2121 Zanker Road, San Jose, CA 95131, USA

E-mail: jeremy.turcaud@coherent.com

## Keywords: Ion Implantation, SiC, Annealing, Resistivity, Temperature

## **Abstract**

This study explores the effects of ion implantation and subsequent annealing on the resistivity of SiC. It investigates how implantation temperature, annealing temperature, and implantation beam current influence the recovery process of lattice damage and the resulting electrical properties. The results can be naturally interpreted in terms of cooperative molecular motions, which rule the structural rearrangements in locally disordered regions.

Our findings indicate that implantation at moderate temperatures, i.e.  $500^{\circ}\text{C}$  -  $650^{\circ}\text{C}$ , strikes an optimal balance between damage creation and recovery, leading to lower resistivity after high-temperature annealing (e.g.,  $1800^{\circ}\text{C}$ ). Higher implantation beam current reduces the duration of implantation, increasing post-implantation disorder, which in turn enhances the effectiveness of subsequent annealing. These results suggest that both the degree of initial disorder and the efficiency of recovery during annealing are critical factors in optimizing the electrical properties of ion-implanted semiconductors.

## INTRODUCTION

Ion implantation is a critical process in semiconductor manufacturing, used to modify the electrical properties of materials by introducing dopants into a crystal lattice. However, this process inherently damages the lattice, necessitating a subsequent annealing step to repair the damage and activate the dopants. This damage induced by ion implantation is dramatically increased in certain semiconductor compound such as SiC, hence necessitating to perform ion implantation at elevated temperature [1].

The effectiveness of the recovery and activation processes during annealing are influenced by several factors, including the implantation temperature, annealing temperature, and implantation beam current.

This study investigates how these variables affect the resistivity of ion-implanted 4H-SiC, with a focus on understanding the role of cooperativity in the recovery of lattice damage [2]. By analyzing the interplay between these factors, we seek to optimize the implantation and annealing conditions to achieve the lowest possible resistivity in the

material, a key determinant of its performance in electronic devices.

#### **EXPERIMENTAL DETAILS**

Samples of n-doped 4H-SiC were subjected to ion implantation using aluminum ions as the dopant The Al density was equal to 10<sup>19</sup> ions.cm<sup>-3</sup> extending 350 nm in depth below the sample surface. The implantation was carried out at temperatures ranging from 350°C to 650°C, with beam currents of 0.1 mA and 1 mA. Post-implantation, the samples underwent annealing at temperatures between 1400°C and 1800°C for durations of 3 to 30 minutes, with the surface protected by a C-cap. Resistivity measurements were performed at room temperature after annealing using circular transfer length method measurements. The data were analyzed to determine the relationship between implantation and annealing conditions and the resulting resistivity. Particular attention was given to identifying the conditions that led to the lowest resistivity, which indicates the most effective dopant activation [3] and recovery of lattice damage.

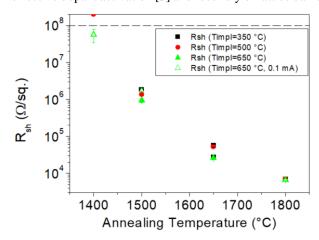

**Figure 1.** Sheet resistance as a function of annealing temperature for different implantation temperatures done at 1mA of beam current except for the last sample done at 0.1mA. The dashed line indicates the upper limit for resistance measurements. The point above this line refers to a sample whose sheet resistance was not measurable.

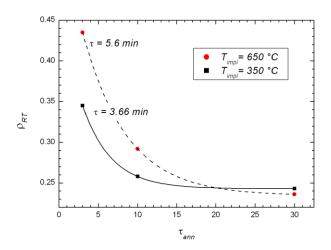

Figure 2.  $\rho_{RT}$  [ $\Omega$  cm] vs.  $\tau_{ann}$  [min] for the 1800 °C annealed samples implanted with the same current but at different implantation temperatures. The fits are single time exponentials.

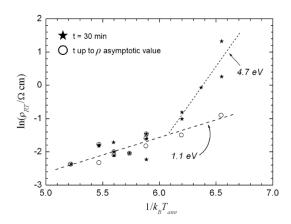

**Figure 3.** 4H-SiC samples Al-implanted with a density  $10^{20}cm^{-3}$  from ref.[3]. Open circles label systems which reached the asymptotic state (no limits on  $\tau_{ann}$ ). Stars label samples annealed for  $\tau_{ann} = 30 \ min$ : the annealing becomes incomplete when  $T_{ann} < 1600 \ ^{\circ}C$ .

### RESULTS

The results demonstrate a clear relationship between the implantation temperature, annealing conditions, and the final resistivity of the material (Fig.1). Fig. 2 gives insight on the damage recovery and activation mechanism as a function of the annealing time. At lower implantation temperatures (350°C), the samples exhibited higher initial disorder, leading to faster recovery during post-implantation annealing. However, this also resulted in fewer successful atomic substitutions, limiting the reduction in final resistivity [4]. In contrast, samples implanted at higher temperatures (500 & 650°C) displayed less initial disorder and lower cooperativity,

resulting in slower relaxation dynamics during annealing. Despite this, these conditions allow for more effective asymptotic recovery during annealing, particularly at lower annealing temperatures (<1800°C), leading to significantly lower resistivity, as shown in Fig.1.

The data indicate that, in the investigated experimental conditions, the combination of a moderate implantation temperature (around 500 to 650°C) and a high annealing temperature (1800°C) provides the optimal conditions for minimizing resistivity. Higher implantation currents, at least up to 1 mA, as investigated here, further reduced resistivity by shortening the implantation time, thereby increasing the post-implantation disorder and enhancing the effectiveness of the subsequent annealing process. Fig.2 also shows that at 1800 °C the time required for a complete annealing might be lower than 30 min, providing room for further optimization. The present result can be explained by the mechanism proposed in ref. [3], and shown in Fig.3 for completeness. As shown in Fig.3, samples annealed at 1650°C for 30 minutes showed incomplete recovery, as evidenced by higher resistivity compared to samples annealed for longer times. The higher resistivity observed in those samples was attributed to the insufficient time or temperature for complete recovery of lattice damage, particularly in regions with higher initial disorder.

#### **CONCLUSION**

This study emphasizes the critical role of implantation temperature, annealing temperature and time, implantation beam current in determining the final resistivity of ion-implanted 4H-SiC. The optimal conditions for achieving the lowest resistivity are an implantation temperature of around 500-650°C and a high annealing temperature of 1800°C for up to 30 minutes. This allows sufficient damage to facilitate recovery during annealing while ensuring effective lattice repair. Higher beam currents up to at least 1 mA, also reduce resistivity by increasing disorder, which enhances recovery. However, lower annealing temperatures (e.g., 1650°C) or shorter times may lead to incomplete recovery and higher resistivity. These findings offer valuable insights for optimizing ion implantation and annealing in SiC device manufacturing, providing a pathway to improve electrical properties through control of processing conditions. careful investigations are underway on the impact of these findings on carrier mobility and performance in more complex SiC devices.

#### REFERENCES

- [1] F. Roccaforte et al., Micro 2, 23–53 (2022)

- [2] M. Pieruccini and E. Tombari, PRE 97, 032116 (2018)

- [3] V. Boldrini, A. Parisini and M. Pieruccini, Mat. Sci. Semicond. Proc. 148, 106825 (2022)

- [4] R. Nipoti and A. Parisini, ECS Transactions 92 (7), 91-98 (2019)